新闻公告

2023年度

晶方科技刘宏钧谈高密度封装和集成工艺|第十六期“芯片大家说”沙龙精彩回顾

2023年6月6日,由张江高科和全球领先的半导体产业智库芯谋研究共同主办的第十六期“芯片大家说I Say IC”产业沙龙成功举行。本期活动成功邀请到苏州晶方半导体科技股份有限公司副总裁刘宏钧,为大家带来“高密度封装和集成工艺”领域的精彩内容。活动现场吸引了50余位产业嘉宾出席。

2023年6月6日,由张江高科和全球领先的半导体产业智库芯谋研究共同主办的第十六期“芯片大家说I Say IC”产业沙龙成功举行。本期活动成功邀请到苏州晶方半导体科技股份有限公司副总裁刘宏钧,为大家带来“高密度封装和集成工艺”领域的精彩内容。活动现场吸引了50余位产业嘉宾出席。

晶方科技副总裁 刘宏钧

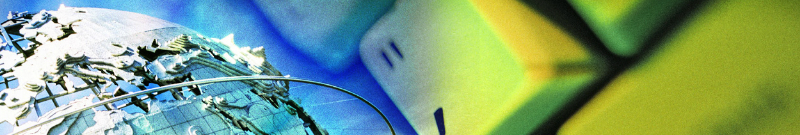

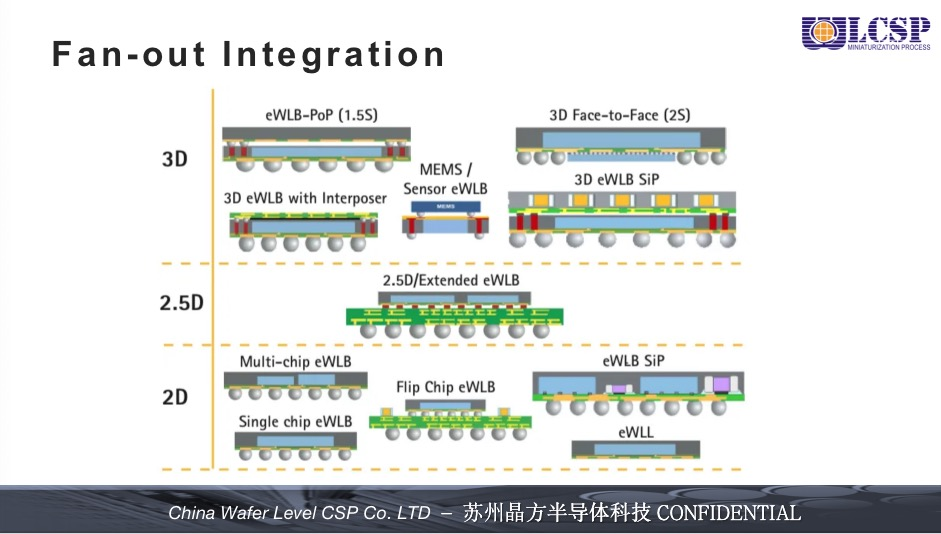

在演讲中,刘宏钧提到5G、物联网、自动驾驶、自动化和人工智能对于半导体系统集成需求巨大,这些应用需要更先进的芯片,具有更低的功耗、更高的速度、更小的外形尺寸和集成的功能。通过封装技术实现超越摩尔定律可以快速推动集成电路向异构集成封装的新高度扩展。后摩尔时代不同技术节点的产品可以放在同一封装体内,也能将不同功能的芯片一起封装,异构集成的发展趋势明显。未来我们可能会看到更多集成处理器、信号处理器、高速缓存、传感器、光电、RF和MEMS的产品设计。受到这些产品应用驱动,先进封装技术正在进入一个快速发展的阶段,异构集成封装,Chiplet芯片设计等方向和市场前景值得行业关注。演讲中,刘宏钧详细介绍了封装微缩和先进互联技术的多种实现手段和工艺特点,包括系统级封装SiP、晶圆级封装WLP、面板级封装PLP等。 刘宏钧提到,近年来,半导体制程特征尺寸缩小越来越困难,摩尔定律是否已经到达极限成为半导体业界乃至整个社会所关注的问题。在尺寸缩微(Scaling)技术推进上,业界有三种思路,“More Moore(深度摩尔)”“More than Moore(超越摩尔)”与“Beyond CMOS(新器件)”。其中,“More Moore(深度摩尔)”路线在想办法沿着摩尔定律的CMOS工艺(CMOS Scaling)道路继续往前推进。“More than Moore(超越摩尔)”做的是通过封装缩微(Packaging Scaling)提升集成的密度。“Beyond CMOS(新器件)”做的开发硅基以外的新型器件。今天的话题主要围绕在“More Moore(深度摩尔)”越来越困难的前提下“More than Moore(超越摩尔)”为行业可能提供的技术路径。 在超越摩尔(Packaging Scaling)的路线上,封装微缩侧重于功能解耦和高密度集成。例如,在一个异质集成系统中实现提升性能的数字处理器/存储模块以及其他模块集成,集成度的提高通过封装技术来实现,而不是将更多功能用同一CMOS工艺在同一晶圆上缩微到同一块芯片中,从而通过封装微缩实现系统级封装SiP。

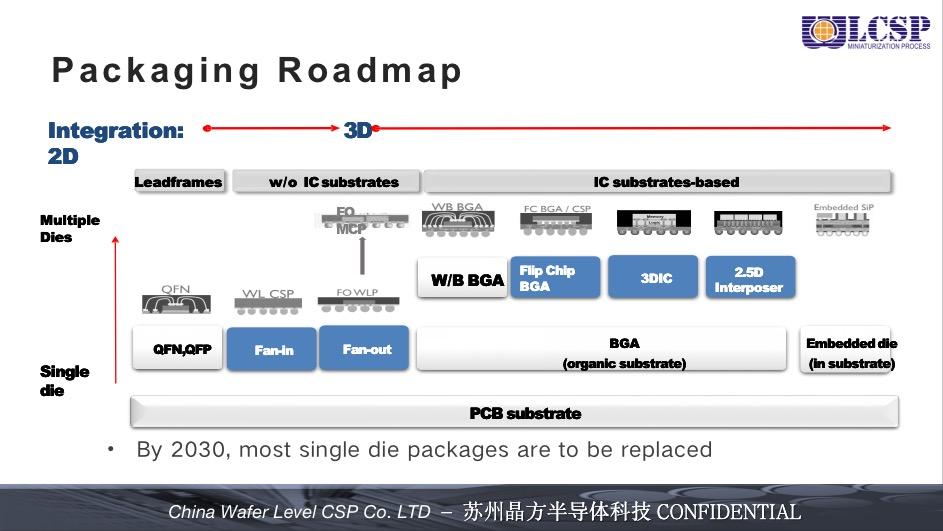

SiP系统级封装系统间各模块通过互连技术实现通信。先进互连技术包括凸块(Bumping)、2.5D的插入器(Interposer)、3D的TSV/TGV/TMV、无凸块混合键合,晶圆级堆叠等工艺和方法。

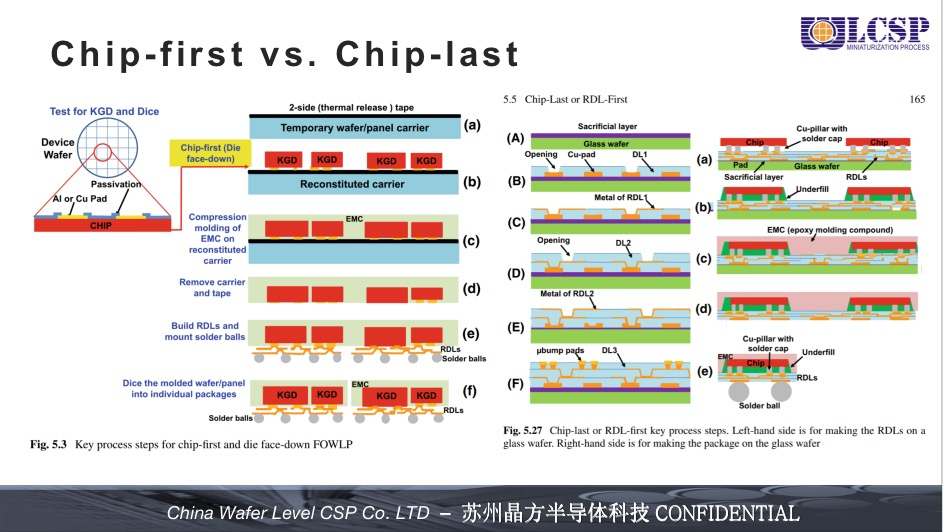

最先进的系统级封装技术会用到晶圆级封装(WLP),WLP技术主要采用重布线层技术、微凸点两大基础技术。WLP的优势在于是一种适用于更小型集成电路的芯片级封装(CSP)技术。它可在晶圆上采用整面封装和电子测试技术,在提高产量的同时显著减少芯片封装面积。

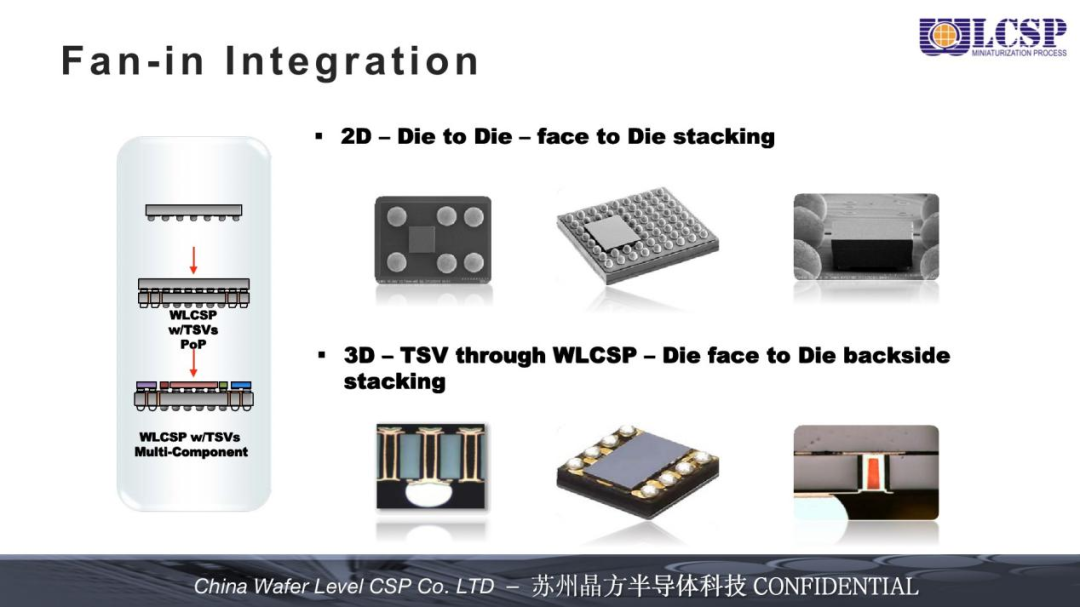

从技术特点上看,晶圆级封装(WLP)主要分为扇入型Fan-in和扇出型Fan-out两种。

SiP系统级封装系统间各模块通过互连技术实现通信。先进互连技术包括凸块(Bumping)、2.5D的插入器(Interposer)、3D的TSV/TGV/TMV、无凸块混合键合,晶圆级堆叠等工艺和方法。

最先进的系统级封装技术会用到晶圆级封装(WLP),WLP技术主要采用重布线层技术、微凸点两大基础技术。WLP的优势在于是一种适用于更小型集成电路的芯片级封装(CSP)技术。它可在晶圆上采用整面封装和电子测试技术,在提高产量的同时显著减少芯片封装面积。

从技术特点上看,晶圆级封装(WLP)主要分为扇入型Fan-in和扇出型Fan-out两种。

传统的WLP封装多采用Fan-in型,应用于低引脚(Pin)数的IC。扇入型Fan-in封装技术拥有最小封装尺寸和低成本相结合的优势,目前主要的扇入型Fan-in封装器件为WiFi/BT(无线局域网、蓝牙)集成组件、收发器、PMIC(电源管理集成电路)和DC/DC转换器,以及包括MEMS和图像传感器在内的各种数字、模拟、混合信号器件。

传统的WLP封装多采用Fan-in型,应用于低引脚(Pin)数的IC。扇入型Fan-in封装技术拥有最小封装尺寸和低成本相结合的优势,目前主要的扇入型Fan-in封装器件为WiFi/BT(无线局域网、蓝牙)集成组件、收发器、PMIC(电源管理集成电路)和DC/DC转换器,以及包括MEMS和图像传感器在内的各种数字、模拟、混合信号器件。

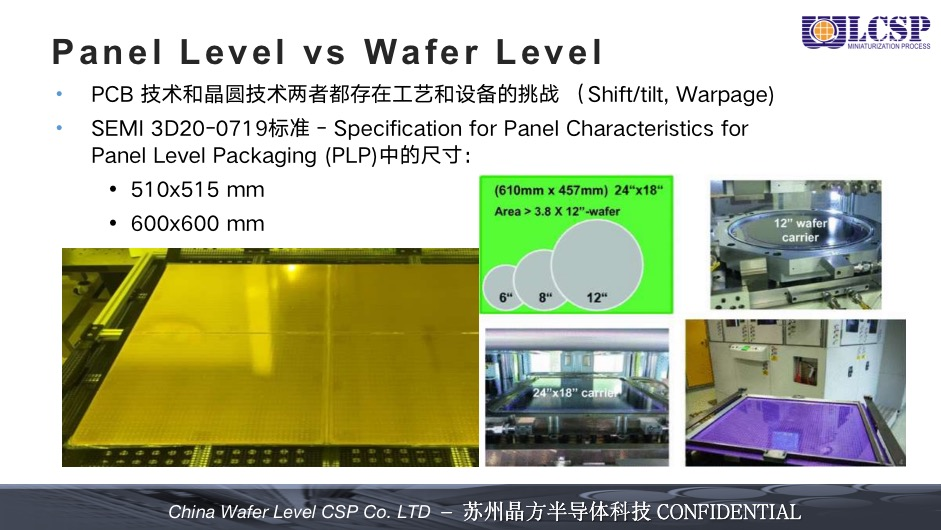

与晶圆级封装(WLP)不同,板级扇出封装(PLP)在圆形尺寸上向更大面积的长方形尺寸拓展,以获得更优的性价比。根据基板材料来分可以归为三类:有机物基板、硅基板、玻璃基板。板级封装工艺流程与晶圆级封装本身没有太大差异,但是需要独立开发生产设备及相应系统。板级封装和晶圆技术两者都存在工艺和设备的挑战,主要是材料CTE造成的应力引起的基板翘曲,以及系统散热等方面问题。板级封装借鉴了很多PCB技术,可以实现多芯片的灵活布局,相比于晶圆级封装更具成本优势潜力。不过,这一领域相关的工艺开发,设备和材料,测试和设计仿真等都有待解决。

在此基础上,业界还继续在探索和完善异质集成(Heterogeneous Integration),即不同工艺节点的芯片可以用封装技术集成在同一封装中,而芯片间的通讯则使用高速接口连接。作为后摩尔时代集成电路发展的新方向,异质集成技术在工艺、性能、材料等方面面对着一系列的挑战。

在封装技术方面,有钱、有客户、有人才的大厂们一直走在最前列。以台积电为例,其封装平台“3D Fabric”被划分为两个部分,“前端”封装技术和“后端”封装技术。前端芯片堆叠技术统称为“SoIC”,即集成芯片系统(System of Integrated Chips),包括CoW(chip-on-wafer)和WoW(wafer-on-wafer)等;后端芯片3D封装则包括了InFo和COWoS等技术,可以在后道工艺中实现不同异质芯片的3D堆叠。英特尔也于2018年提出先进的2.5D和3D封装技术,并推出了Foveros异构平台。使用Foveros技术,在二维平面上可以通过EMIB实现裸芯片之间的互联,在三维垂直方向上使用TSV(Through Silicon Via)实现裸芯片之间的堆叠。AMD的Zen架构&Infinity Fabric也实现了出色的可扩展性,AMD在x86处理器中大胆采用全新理念:Chiplet小芯片。AMD没有构建更大、更昂贵的单片芯片,而是采取了称为小芯片的处理器构建块。每个小芯片都包含许多基于“Zen”的核心,而且封装的小芯片越多,处理器性能就越强。目前“Zen”处理器的核心数少则两个,多则128个。通过封装内AMD Infinity Fabric接口实现DIE-TO-DIE的低功耗,高速率连接。

异构集成所带来的Chiplet(小芯片)概念是业内近年业界最火热的技术趋势之一。Chiplet小芯片可视为固定模块,在不同的产品中根据需求进行灵活组装,类似乐高积木,具有极强的复用性。通过小芯片化设计可以实现IP芯片化,不仅可以减少芯片的设计周期,加快迭代速度,还可以提高芯片的可定制性。通过Chiplet方式,多个小芯片无需重复设计,具有复用价值,而且芯片可采用最合适的工艺制程,可有效提高良率以及降低设计门槛。Chiplet的技术路径在可定制性、设计周期、降低成本方面有极大的优化空间。

刘宏钧认为,大算力芯片将会是Chiplet规模应用最具确定性的市场。为了统一Chiplet之间的互连接口标准,打造一个开放性的Chiplet生态系统,Intel、AMD、ARM、高通、三星、台积电、日月光、Google Cloud、Meta和微软等公司联合推出的Die-to-Die互连标准UCIe。UCIe主要包括协议层(Protocol Layer)、适配层(Adapter Layer)和物理层(Physical Layer)。协议层把数据转换成Flit包进行传输;适配层在协议层和物理层中间,当协议层有多个协议同时工作时,ARB/MUX用来在多个协议之间进行选择和仲裁;物理层主要用来解析Flit包在UCIe Data Lane上进行传输。

演讲最后,刘宏钧也对晶方科技做了简短介绍。作为国内高端封装技术创新型企业,晶方科技提供WLCSP和FO扇出结构为基础的高集成度,微型化的半导体先进封装量产服务。晶方科技长期专注于传感器芯片的先进封装技术,封装产品包括多种影像传感器芯片(CIS),屏下指纹识别芯片,3D成像,微机电系统芯片(MEMS)、环境光感应芯片、5G射频芯片等产品。面对国内封装市场在设备和材料上面对的挑战,刘宏钧表示,发展先进封装技术,产业链也面临挑战,封测企业与设备厂商必须密切协同,共生共赢,人才资源不足的现象,亟待高校、企业乃至行业机构能够携手破解。同时,他也指出国内产业界拥有着巨大热情,对产业链整合充满信心,相信在先进封装领域国内终将探索出一条适合自身特点的发展道路。

演讲过后,芯谋研究高级分析师蒋思莹担任主持人开启现场问答环节,晶方科技副总裁刘宏钧回答了现场观众关于封装技术与市场未来的诸多关切问题。本场沙龙在现场热烈的互动下圆满结束。

与晶圆级封装(WLP)不同,板级扇出封装(PLP)在圆形尺寸上向更大面积的长方形尺寸拓展,以获得更优的性价比。根据基板材料来分可以归为三类:有机物基板、硅基板、玻璃基板。板级封装工艺流程与晶圆级封装本身没有太大差异,但是需要独立开发生产设备及相应系统。板级封装和晶圆技术两者都存在工艺和设备的挑战,主要是材料CTE造成的应力引起的基板翘曲,以及系统散热等方面问题。板级封装借鉴了很多PCB技术,可以实现多芯片的灵活布局,相比于晶圆级封装更具成本优势潜力。不过,这一领域相关的工艺开发,设备和材料,测试和设计仿真等都有待解决。

在此基础上,业界还继续在探索和完善异质集成(Heterogeneous Integration),即不同工艺节点的芯片可以用封装技术集成在同一封装中,而芯片间的通讯则使用高速接口连接。作为后摩尔时代集成电路发展的新方向,异质集成技术在工艺、性能、材料等方面面对着一系列的挑战。

在封装技术方面,有钱、有客户、有人才的大厂们一直走在最前列。以台积电为例,其封装平台“3D Fabric”被划分为两个部分,“前端”封装技术和“后端”封装技术。前端芯片堆叠技术统称为“SoIC”,即集成芯片系统(System of Integrated Chips),包括CoW(chip-on-wafer)和WoW(wafer-on-wafer)等;后端芯片3D封装则包括了InFo和COWoS等技术,可以在后道工艺中实现不同异质芯片的3D堆叠。英特尔也于2018年提出先进的2.5D和3D封装技术,并推出了Foveros异构平台。使用Foveros技术,在二维平面上可以通过EMIB实现裸芯片之间的互联,在三维垂直方向上使用TSV(Through Silicon Via)实现裸芯片之间的堆叠。AMD的Zen架构&Infinity Fabric也实现了出色的可扩展性,AMD在x86处理器中大胆采用全新理念:Chiplet小芯片。AMD没有构建更大、更昂贵的单片芯片,而是采取了称为小芯片的处理器构建块。每个小芯片都包含许多基于“Zen”的核心,而且封装的小芯片越多,处理器性能就越强。目前“Zen”处理器的核心数少则两个,多则128个。通过封装内AMD Infinity Fabric接口实现DIE-TO-DIE的低功耗,高速率连接。

异构集成所带来的Chiplet(小芯片)概念是业内近年业界最火热的技术趋势之一。Chiplet小芯片可视为固定模块,在不同的产品中根据需求进行灵活组装,类似乐高积木,具有极强的复用性。通过小芯片化设计可以实现IP芯片化,不仅可以减少芯片的设计周期,加快迭代速度,还可以提高芯片的可定制性。通过Chiplet方式,多个小芯片无需重复设计,具有复用价值,而且芯片可采用最合适的工艺制程,可有效提高良率以及降低设计门槛。Chiplet的技术路径在可定制性、设计周期、降低成本方面有极大的优化空间。

刘宏钧认为,大算力芯片将会是Chiplet规模应用最具确定性的市场。为了统一Chiplet之间的互连接口标准,打造一个开放性的Chiplet生态系统,Intel、AMD、ARM、高通、三星、台积电、日月光、Google Cloud、Meta和微软等公司联合推出的Die-to-Die互连标准UCIe。UCIe主要包括协议层(Protocol Layer)、适配层(Adapter Layer)和物理层(Physical Layer)。协议层把数据转换成Flit包进行传输;适配层在协议层和物理层中间,当协议层有多个协议同时工作时,ARB/MUX用来在多个协议之间进行选择和仲裁;物理层主要用来解析Flit包在UCIe Data Lane上进行传输。

演讲最后,刘宏钧也对晶方科技做了简短介绍。作为国内高端封装技术创新型企业,晶方科技提供WLCSP和FO扇出结构为基础的高集成度,微型化的半导体先进封装量产服务。晶方科技长期专注于传感器芯片的先进封装技术,封装产品包括多种影像传感器芯片(CIS),屏下指纹识别芯片,3D成像,微机电系统芯片(MEMS)、环境光感应芯片、5G射频芯片等产品。面对国内封装市场在设备和材料上面对的挑战,刘宏钧表示,发展先进封装技术,产业链也面临挑战,封测企业与设备厂商必须密切协同,共生共赢,人才资源不足的现象,亟待高校、企业乃至行业机构能够携手破解。同时,他也指出国内产业界拥有着巨大热情,对产业链整合充满信心,相信在先进封装领域国内终将探索出一条适合自身特点的发展道路。

演讲过后,芯谋研究高级分析师蒋思莹担任主持人开启现场问答环节,晶方科技副总裁刘宏钧回答了现场观众关于封装技术与市场未来的诸多关切问题。本场沙龙在现场热烈的互动下圆满结束。